Table of Contents

Design Notes on a Audio Synthesizer Design

Phase Accumulators

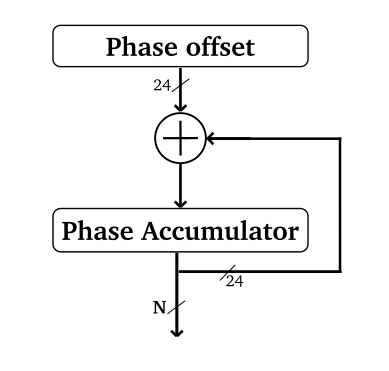

A common digital technique to generate very specific frequencies is to use what is called phase accumulation. The idea of a phase accumulator is to add a fraction of a cycle to the phase on each clock edge such that the accumulated phase reaches one (one full cycle) at the right time.

A common digital technique to generate very specific frequencies is to use what is called phase accumulation. The idea of a phase accumulator is to add a fraction of a cycle to the phase on each clock edge such that the accumulated phase reaches one (one full cycle) at the right time.

Let's use an example that is specific to this design. Let's say our audio update rate is 100 KHz. This gives use 10 microseconds per audio sample to the output DAC. The note C0 is 16.35 Hertz. In one sample a C0 note will change its phase by

(16.35 / 100000) = 0.0001635 cycle

This is 0.000000000000101010110111 as a binary fraction, and this is what we would add to the accumulator every 10 microseconds to get 16.35 Hz output. Showing the phase offset as binary helps get across the idea that a hundredth of a cycle at 16.35 Hertz needs 24 bits of precision.

The FPGA never sees the note C0 or the frequency. All it sees is the phase offset per sample and this is set by a look-up table in the host. Feeding the MSB of the phase accumulator to an output pin is a minimal tone generator.

Wave Tables

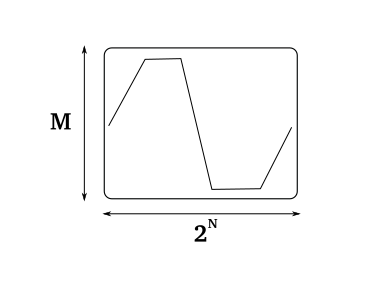

A wave table captures a waveform by dividing it into slices and recording the output value for each slice. If the address decoder has N bits then the length of the table is 2^N. A wave table is usually driven by the N high bits of a phase accumulator.

A wave table captures a waveform by dividing it into slices and recording the output value for each slice. If the address decoder has N bits then the length of the table is 2^N. A wave table is usually driven by the N high bits of a phase accumulator.

The number of bits in each word determine the audio fidelity of the output. The values in the table are often the sign and the log of the desired value. Human hearing is such that perceived volume follows a logarithmic scale, and using log value makes subsequent gain and modulations easier since multiplication in a linear scale is just addition in a log scale. You can get the best fidelity from the least number of bits by making the waveform span the full range of M bits. The log function can be log-base-2, natural logarithm, or one of the standard u-law or a-law functions.

There are often more than one wave table and while each may have a default, all can be set from the host. The API is to be determined but might appear something like:

dpset tonegen table_id 3 # select the table to download dpset tonegen table_addr 0 # point to first address in table dpset tonegen table_val 00 12 34 56 78 9a 87 56 78 88 99 aa bb cc dd ee dpset tonegen table_val ff ee ff ee ff ee ff ee ff ee ff ee ff ee ff ee (... for all 2^N values ...)

Gain Blocks

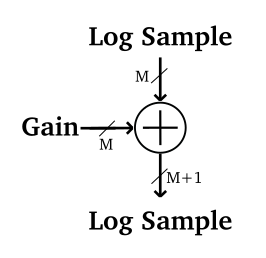

As mentioned above, gain is just addition when using log amplitude values. You have a few choices when dealing with the issue of overflow. One approach is to increase the sample size at each addition. This is shown in the diagram at the right. This approach maintains the greatest fidelity through the system at the expense of consuming more FPGA fabric. Another approach is to use saturating arithmetic. Saturating addition prevent overflow by clipping the output to a maximum value. For example, in 8 bits the value of

As mentioned above, gain is just addition when using log amplitude values. You have a few choices when dealing with the issue of overflow. One approach is to increase the sample size at each addition. This is shown in the diagram at the right. This approach maintains the greatest fidelity through the system at the expense of consuming more FPGA fabric. Another approach is to use saturating arithmetic. Saturating addition prevent overflow by clipping the output to a maximum value. For example, in 8 bits the value of FF+1 would not be zero but remain at FF.

Another consideration is the meaning of gain. If the values in the wave tables represent the smallest signal then gain means amplification. It the value represent the loudest samples possible then gain means attenuation and the gain block is actually subtraction.

To Do

- vibrado and portamento

- tremelo

- white and pink noise generators

- ADSR envelop design

- voices and channels

- FIFO for notes to be played